## PSoC<sup>™</sup> Mixed Signal Array Preliminary Data Sheet For Silicon Revision A

### **December 22, 2003**

Cypress MicroSystems 2700 162nd Street SW Building D Lynnwood, WA 98037 Phone: 800.669.0557 FAX: 425.787.4641 http://www.cypress.com

Document No. 38-12011 Rev. \*E

| CY8C24xxx Preliminary Data Sheet |

|----------------------------------|

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

|                                  |

© Cypress MicroSystems, Inc. 2000 -2003. All rights reserved. PSoC<sup>™</sup> (Programmable System-on-Chip<sup>™</sup>) is a trademark of Cypress MicroSystems, Inc. All other trademarks or registered trademarks referenced herein are property of the respective corporations.

The information contained herein is subject to change without notice. Cypress MicroSystems assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress MicroSystems product. Nor does it convey or imply any license under patent or other rights. Cypress MicroSystems does not authorize its products for use as critical components in life support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress MicroSystems' products in life-support system applications implies that the manufacturer assumes all risk of such use and in doing so, indemnifies Cypress MicroSystems against all charges.

# Contents

|            | ION A OVERVIEW                                                                                                                                                                                                                                                                                                                                   | 13                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|            | Features                                                                                                                                                                                                                                                                                                                                         | 13                                        |

|            | Getting Started                                                                                                                                                                                                                                                                                                                                  | 14                                        |

|            | Development Kits                                                                                                                                                                                                                                                                                                                                 | 14                                        |

|            | Tele-Training                                                                                                                                                                                                                                                                                                                                    |                                           |

|            | Consultants                                                                                                                                                                                                                                                                                                                                      | 14                                        |

|            | Technical Support                                                                                                                                                                                                                                                                                                                                | 14                                        |

|            | Application Notes                                                                                                                                                                                                                                                                                                                                | 14                                        |

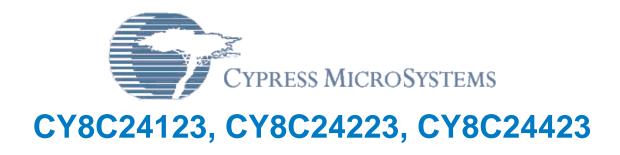

|            | Top-Level Architecture                                                                                                                                                                                                                                                                                                                           | 15                                        |

|            | Development Tools                                                                                                                                                                                                                                                                                                                                |                                           |

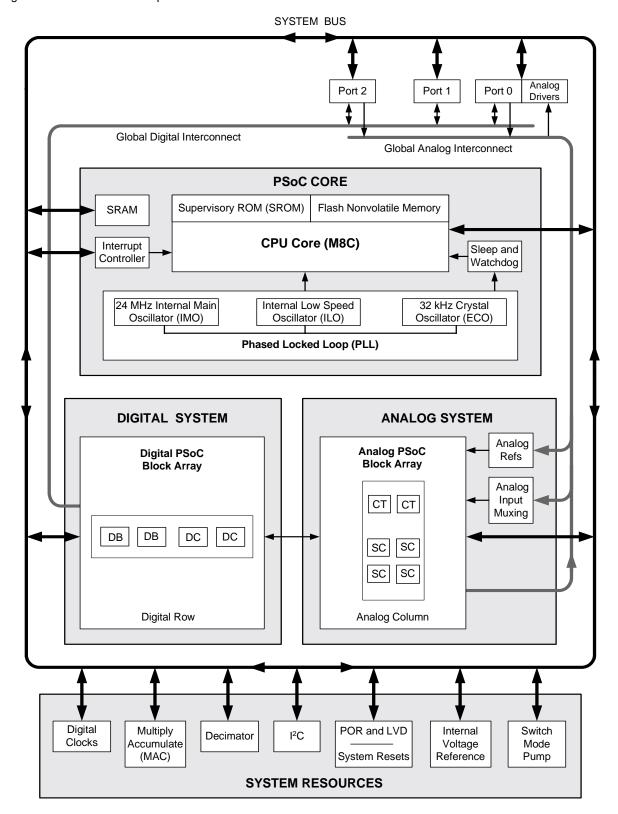

|            | PSoC Designer Software Subsystems                                                                                                                                                                                                                                                                                                                | 16                                        |

|            | Hardware Tools                                                                                                                                                                                                                                                                                                                                   |                                           |

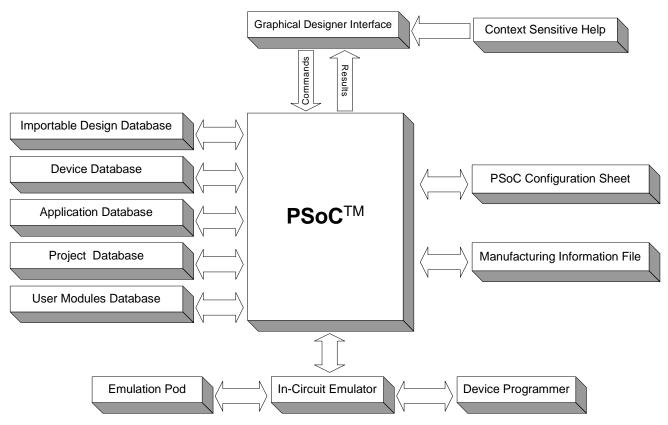

|            | User Modules and Development Process                                                                                                                                                                                                                                                                                                             |                                           |

|            | Ordering Information                                                                                                                                                                                                                                                                                                                             |                                           |

|            | Organization and Conventions                                                                                                                                                                                                                                                                                                                     |                                           |

|            | Document Organization                                                                                                                                                                                                                                                                                                                            |                                           |

|            | Document Conventions                                                                                                                                                                                                                                                                                                                             | 20                                        |

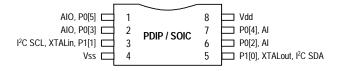

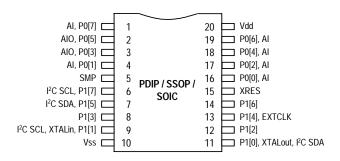

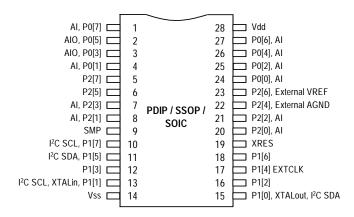

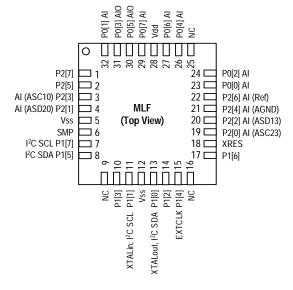

| 1.         | Pin Information                                                                                                                                                                                                                                                                                                                                  | 23                                        |

|            | 1.1 Pin Summary                                                                                                                                                                                                                                                                                                                                  | 23                                        |

|            | 1.2 Pinouts                                                                                                                                                                                                                                                                                                                                      | 24                                        |

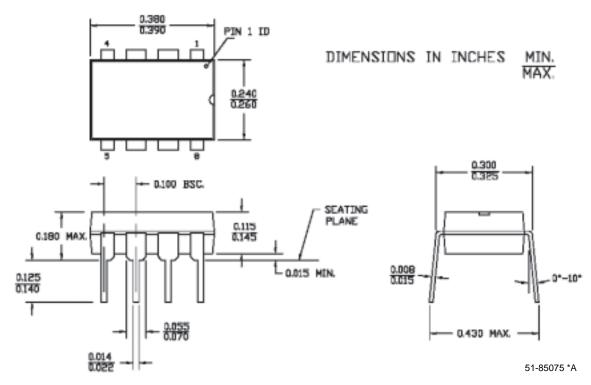

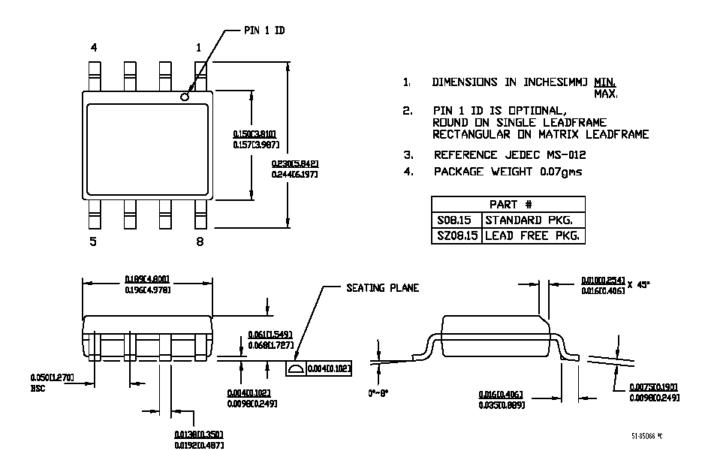

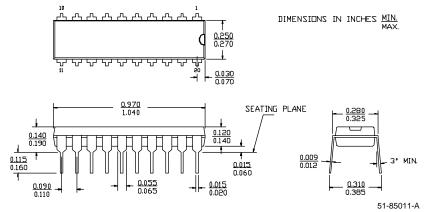

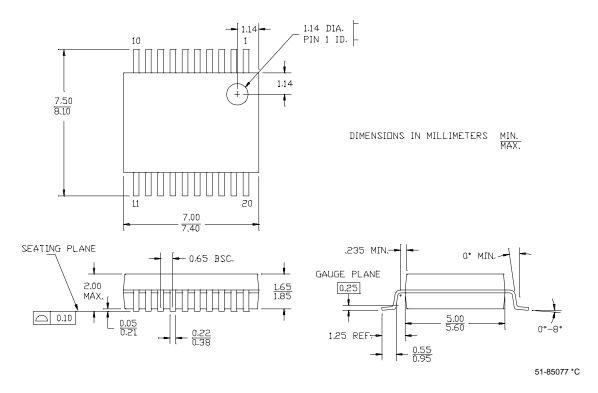

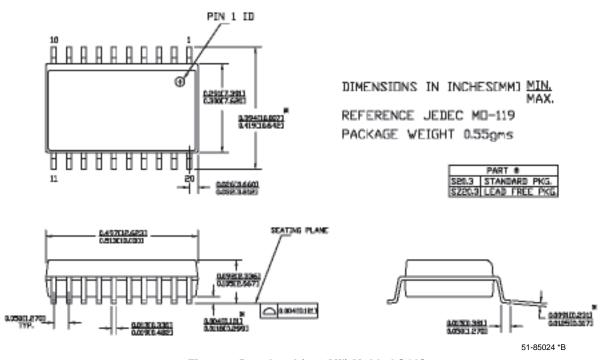

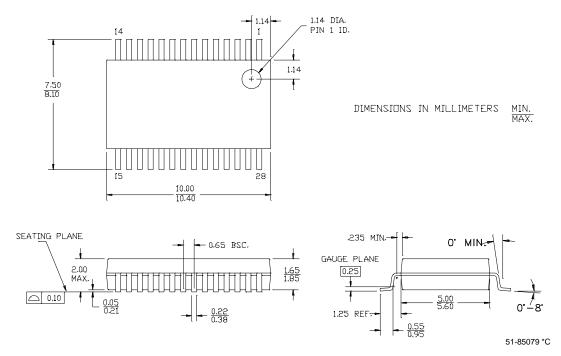

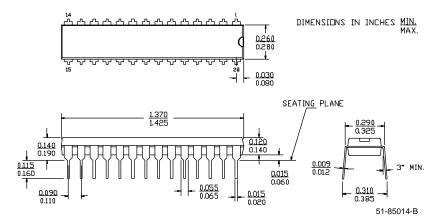

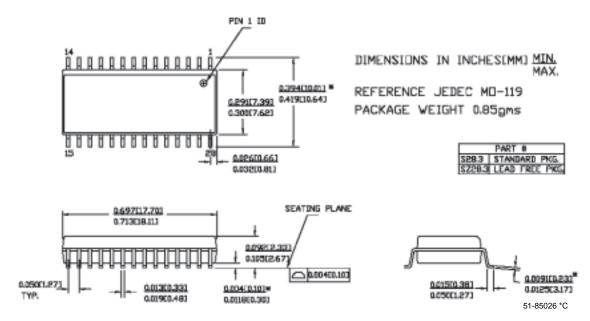

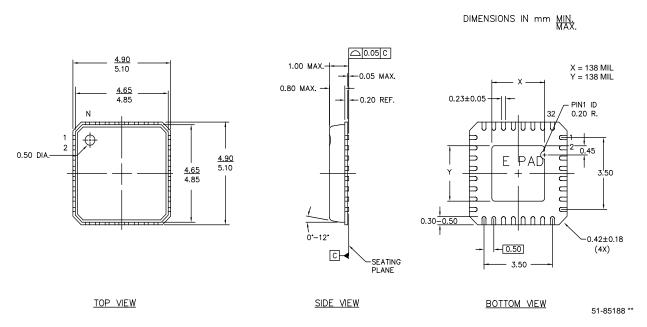

| 2.         | Packaging Information                                                                                                                                                                                                                                                                                                                            | 27                                        |

|            | 2.1 Packaging Dimensions                                                                                                                                                                                                                                                                                                                         | 27                                        |

|            |                                                                                                                                                                                                                                                                                                                                                  |                                           |

|            | 2.2 Thermal Impedances                                                                                                                                                                                                                                                                                                                           |                                           |

| SECTI      | 2.2 Thermal Impedances                                                                                                                                                                                                                                                                                                                           | 32                                        |

| SECTION    | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE                                                                                                                                                                                                                                                                                                  | 32<br><b>33</b>                           |

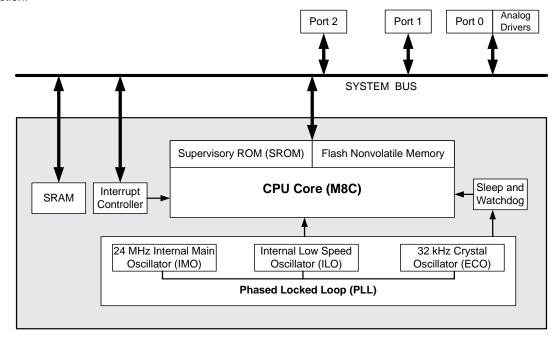

| SECTIO     | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE  Top-Level Core Architecture                                                                                                                                                                                                                                                                     | 32<br><b>33</b><br>33                     |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE  Top-Level Core Architecture  Core Register Summary                                                                                                                                                                                                                                              |                                           |

| SECTION 3. | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE  Top-Level Core Architecture  Core Register Summary                                                                                                                                                                                                                                              |                                           |

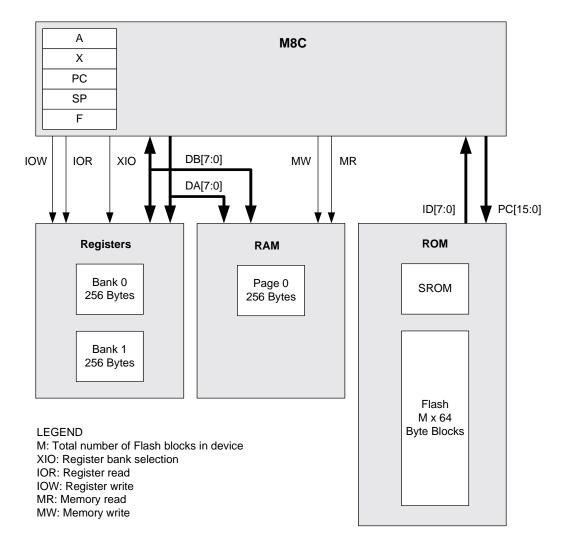

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE  Top-Level Core Architecture  Core Register Summary  CPU Core (M8C)  3.1 Internal Registers                                                                                                                                                                                                      |                                           |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE  Top-Level Core Architecture  Core Register Summary  CPU Core (M8C)  3.1 Internal Registers  3.2 Address Spaces                                                                                                                                                                                  |                                           |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary                                                                                                                                                          |                                           |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format                                                                                                                                   |                                           |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions                                                                                                       |                                           |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions                                                                           | 33 33 34 37 37 37 39 40 40                |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions 3.4.3 Three-Byte Instructions                                             | 33 33 34 37 37 37 37 40 40 40             |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions 3.4.3 Three-Byte Instructions 3.5 Addressing Modes                        | 33 33 34 37 37 37 37 40 40 40 41          |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions 3.4.3 Three-Byte Instructions 3.5 Addressing Modes 3.5.1 Source Immediate | 33 33 34 37 37 37 39 40 40 41 41          |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format  3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions 3.4.3 Three-Byte Instructions 3.5.1 Source Immediate 3.5.1 Source Direct | 33 33 34 37 37 39 40 40 41 41 41          |

|            | 2.2 Thermal Impedances  ION B CORE ARCHITECTURE Top-Level Core Architecture Core Register Summary  CPU Core (M8C) 3.1 Internal Registers 3.2 Address Spaces 3.3 Instruction Set Summary 3.4 Instruction Format 3.4.1 One-Byte Instructions 3.4.2 Two-Byte Instructions 3.4.3 Three-Byte Instructions 3.5 Addressing Modes 3.5.1 Source Immediate | 33 33 34 37 37 37 39 40 40 40 41 41 41 42 |

|     |            | 3.5.5<br>3.5.6<br>3.5.7<br>3.5.8<br>3.5.9 | Destination Indexed  Destination Direct Source Immediate  Destination Indexed Source Immediate  Destination Direct Source Direct  Source Indirect Post Increment | 43<br>44<br>44 |

|-----|------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     | 3.6        | 3.5.10<br>Register Def<br>3.6.1           | Destination Indirect Post IncrementinitionsCPU_F (Flag) Register                                                                                                 | 45             |

| 4.  | Supervi    | sory ROM (S                               | SROM)                                                                                                                                                            | 47             |

|     | 4.1        | Architectural                             | Description                                                                                                                                                      | 47             |

|     |            | 4.1.1                                     | Additional SROM Feature                                                                                                                                          |                |

|     | 4.0        | 4.1.2                                     | SROM Function Descriptions                                                                                                                                       |                |

|     | 4.2        | Register Det<br>4.2.1                     | initions                                                                                                                                                         |                |

|     | 4.3        |                                           | CPU_SCR1 Register                                                                                                                                                |                |

| _   |            | J                                         |                                                                                                                                                                  |                |

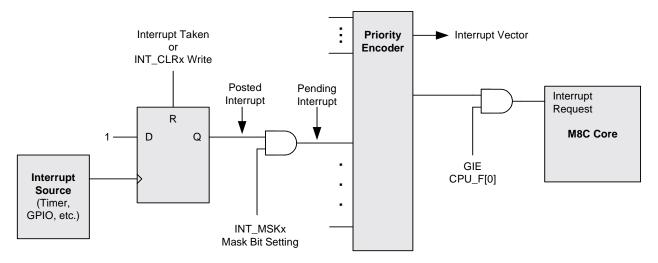

| 5.  | -          |                                           | Description                                                                                                                                                      |                |

|     | 5.1<br>5.2 |                                           | Descriptioninitions                                                                                                                                              |                |

|     | 3.2        | 5.2.1                                     | INT_CLRx Register                                                                                                                                                |                |

|     |            | 5.2.2                                     | INT_MSKx Register                                                                                                                                                |                |

|     |            | 5.2.3                                     | INT_VC Register                                                                                                                                                  |                |

|     |            | 5.2.4                                     | CPU_F Register                                                                                                                                                   |                |

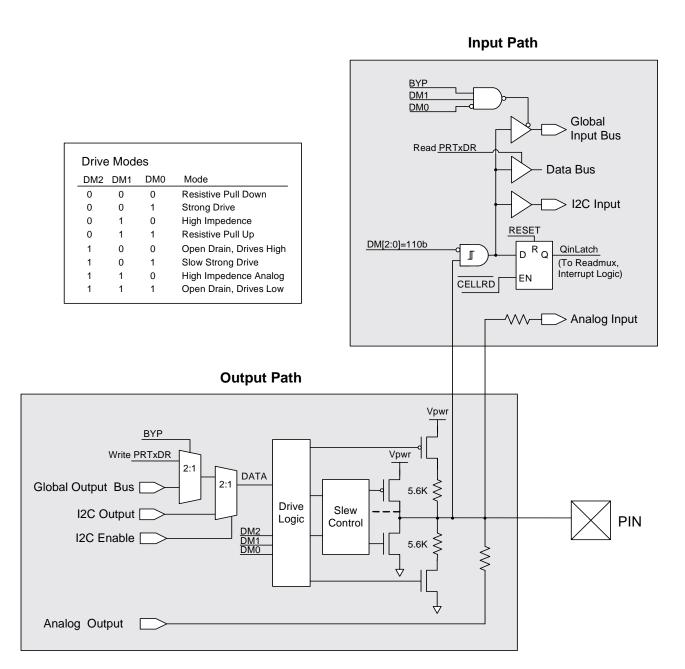

| 6.  | Genera     | l Purnosa IC                              | (GPIO)                                                                                                                                                           | 57             |

| 0.  | 6.1        |                                           | Description                                                                                                                                                      |                |

|     | 0.1        | 6.1.1                                     | Digital IO                                                                                                                                                       |                |

|     |            | 6.1.2                                     | Global IO                                                                                                                                                        |                |

|     |            | 6.1.3                                     | Analog IO                                                                                                                                                        |                |

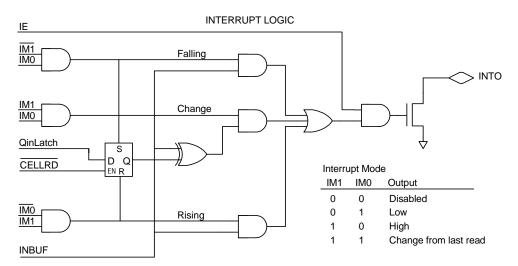

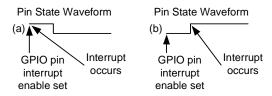

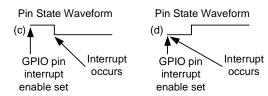

|     |            | 6.1.4                                     | GPIO Block Interrupts                                                                                                                                            | 58             |

|     | 6.2        | •                                         | initions                                                                                                                                                         |                |

|     |            | 6.2.1                                     | PRTxDR Registers                                                                                                                                                 |                |

|     |            | 6.2.2                                     | PRTxIE Registers                                                                                                                                                 |                |

|     |            | 6.2.3<br>6.2.4                            | PRTxDMx Pogistors                                                                                                                                                |                |

|     |            | 6.2.4<br>6.2.5                            | PRTxDMx Registers PRTxICx Registers                                                                                                                              |                |

|     |            |                                           |                                                                                                                                                                  |                |

| 7.  | •          |                                           | ers                                                                                                                                                              |                |

|     | 7.1        |                                           | Description                                                                                                                                                      |                |

|     | 7.2        | Register De                               | finitionsABF_CR0 Register                                                                                                                                        |                |

|     |            |                                           | •                                                                                                                                                                |                |

| 8.  |            |                                           | ator (IMO)                                                                                                                                                       |                |

|     | 8.1        |                                           | Description                                                                                                                                                      |                |

|     | 8.2        | -                                         | initions                                                                                                                                                         |                |

|     |            | 8.2.1                                     | IMO_TR Register                                                                                                                                                  |                |

| 9.  | Internal   |                                           | Oscillator (ILO)                                                                                                                                                 |                |

|     | 9.1        |                                           | Description                                                                                                                                                      |                |

|     | 9.2        | •                                         | initions                                                                                                                                                         |                |

|     |            | 9.2.1                                     | ILO_TR Register                                                                                                                                                  |                |

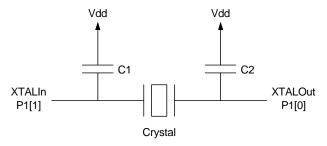

| 10. |            |                                           | llator (ECO)                                                                                                                                                     |                |

|     | 10.1       |                                           | Description                                                                                                                                                      |                |

|     | 40.0       | 10.1.1                                    | ECO External Components                                                                                                                                          |                |

|     | 10.2       | Register Def                              | initions                                                                                                                                                         |                |

|        |                                        | 10.2.1                                                                                                                                                                                                | OSC_CR0 Register                                                                                                                                                           | /0                                                                   |

|--------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|        |                                        | 10.2.2                                                                                                                                                                                                | ECO_TR Register                                                                                                                                                            | 71                                                                   |

|        |                                        | 10.2.3                                                                                                                                                                                                | CPU_SCR1 Register                                                                                                                                                          | 71                                                                   |

| 11     | Dhaca I                                | ocked Loon                                                                                                                                                                                            | ) (PLL)                                                                                                                                                                    | 72                                                                   |

|        | 11.1                                   | Architectural                                                                                                                                                                                         | Description                                                                                                                                                                | 73<br>72                                                             |

|        | 11.2                                   |                                                                                                                                                                                                       | finitions                                                                                                                                                                  |                                                                      |

|        | 11.2                                   | 11.2.1                                                                                                                                                                                                | OSC_CR0 Register                                                                                                                                                           |                                                                      |

|        |                                        | 11.2.2                                                                                                                                                                                                | OSC_CR2 Register                                                                                                                                                           |                                                                      |

|        |                                        |                                                                                                                                                                                                       | •                                                                                                                                                                          |                                                                      |

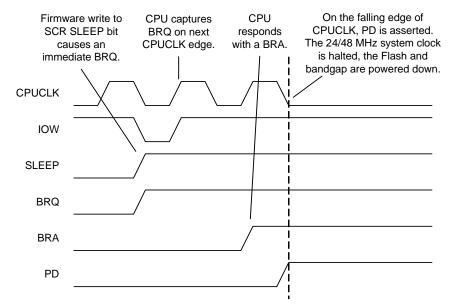

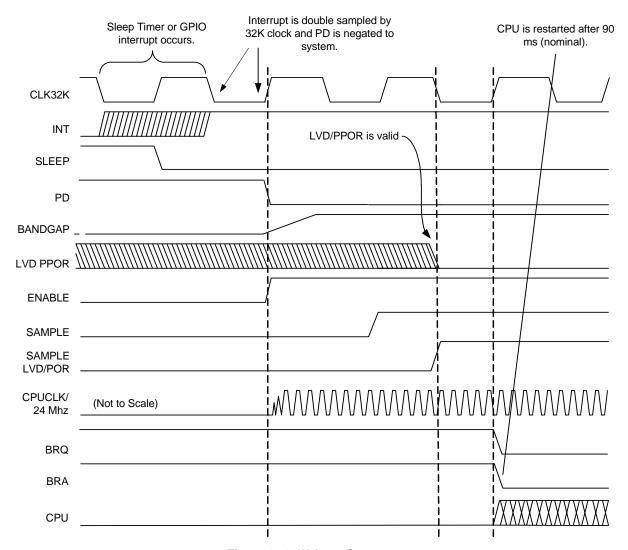

| 12.    | Sleep a                                |                                                                                                                                                                                                       | g                                                                                                                                                                          |                                                                      |

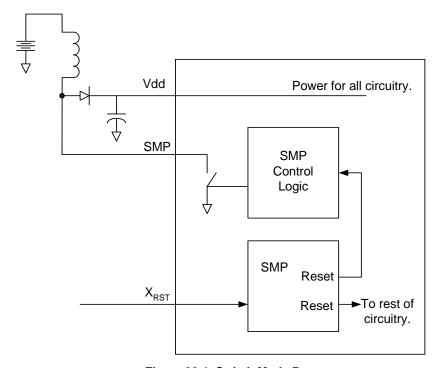

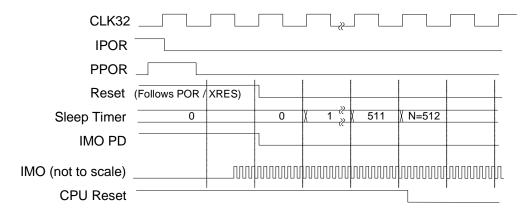

|        | 12.1                                   | Architectural                                                                                                                                                                                         | Description                                                                                                                                                                | 75                                                                   |

|        |                                        | 12.1.1                                                                                                                                                                                                | 32 kHz Clock Selection                                                                                                                                                     |                                                                      |

|        |                                        | 12.1.2                                                                                                                                                                                                | Sleep Timer                                                                                                                                                                |                                                                      |

|        |                                        | 12.1.3                                                                                                                                                                                                | Sleep Bit                                                                                                                                                                  |                                                                      |

|        | 12.2                                   |                                                                                                                                                                                                       | Description                                                                                                                                                                |                                                                      |

|        | 12.3                                   | •                                                                                                                                                                                                     | finitions                                                                                                                                                                  |                                                                      |

|        |                                        | 12.3.1                                                                                                                                                                                                | INT_MSK0 Register                                                                                                                                                          |                                                                      |

|        |                                        | 12.3.2                                                                                                                                                                                                | RES_WDT Register                                                                                                                                                           |                                                                      |

|        |                                        | 12.3.3                                                                                                                                                                                                | OSC_CR0 Register                                                                                                                                                           |                                                                      |

|        |                                        | 12.3.4                                                                                                                                                                                                | CPU_SCR1 Register                                                                                                                                                          |                                                                      |

|        |                                        | 12.3.5                                                                                                                                                                                                | ILO_TR Register                                                                                                                                                            |                                                                      |

|        |                                        | 12.3.6                                                                                                                                                                                                | ECO_TR Register                                                                                                                                                            |                                                                      |

|        |                                        | 12.3.7                                                                                                                                                                                                | CPU_SCR0 Register                                                                                                                                                          |                                                                      |

|        | 12.4                                   |                                                                                                                                                                                                       | rams                                                                                                                                                                       |                                                                      |

|        |                                        | 12.4.1                                                                                                                                                                                                | Sleep Sequence                                                                                                                                                             |                                                                      |

|        |                                        | 12.4.2                                                                                                                                                                                                | Wake Up Sequence                                                                                                                                                           |                                                                      |

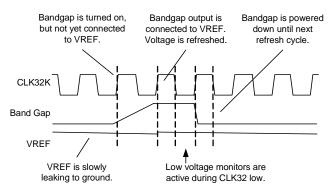

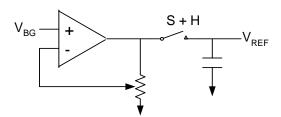

|        |                                        | 12.4.3                                                                                                                                                                                                | Bandgap Refresh                                                                                                                                                            |                                                                      |

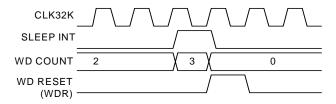

|        |                                        | 12.4.4                                                                                                                                                                                                | Watchdog Timer (WDT)                                                                                                                                                       | 81                                                                   |

|        | 40 -                                   |                                                                                                                                                                                                       |                                                                                                                                                                            |                                                                      |

|        | 12.5                                   | Power Cons                                                                                                                                                                                            | umption                                                                                                                                                                    | 82                                                                   |

| SECTIO |                                        |                                                                                                                                                                                                       |                                                                                                                                                                            |                                                                      |

| SECTIO | N C RE                                 | GISTER REF                                                                                                                                                                                            | ERENCE                                                                                                                                                                     | 83                                                                   |

| SECTIC | N C REG                                | GISTER REF<br>er Convention                                                                                                                                                                           | ERENCE<br>s                                                                                                                                                                | <b>83</b><br>83                                                      |

| SECTIC | N C REG                                | GISTER REF<br>er Convention<br>er Mapping Ta                                                                                                                                                          | ERENCE<br>sables                                                                                                                                                           | <b>83</b><br>83                                                      |

| SECTIO | N C REG                                | GISTER REF<br>er Convention<br>er Mapping Ta<br>Register                                                                                                                                              | SERENCE sables Map 0 Table: User Space                                                                                                                                     |                                                                      |

|        | N C REG<br>Regist<br>Regist            | GISTER REF<br>er Convention<br>er Mapping Ta<br>Register<br>Register                                                                                                                                  | ERENCE sables Map 0 Table: User Space Map 1 Table: Configuration Space                                                                                                     | <b>83</b><br>83<br>84<br>84                                          |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF<br>er Convention<br>er Mapping Ta<br>Register<br>Register                                                                                                                                  | ERENCE sables Map 0 Table: User Space Map 1 Table: Configuration Space                                                                                                     |                                                                      |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi                                                                                                                    | SERENCE sables Map 0 Table: User Space Map 1 Table: Configuration Space sters                                                                                              |                                                                      |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1                                                                                                          | s                                                                                                                                                                          | <b>83</b>                                                            |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2                                                                                                | ERENCE s                                                                                                                                                                   | <b>83</b> 83 83 84 85 <b>87</b> 88 88                                |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3                                                                                      | ERENCE s ables Map 0 Table: User Space Map 1 Table: Configuration Space sters PRTxDR PRTxIE PRTxGS                                                                         | <b>83</b> 83 83 84 85 <b>87</b> 88 88                                |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4                                                                            | ERENCE s                                                                                                                                                                   | <b>83</b> 83 84 85 <b>87</b> 88 88 89 90                             |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5                                                                  | ERENCE s                                                                                                                                                                   | 83 83 84 85 85 87 88 88 89 90                                        |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.1.6                                                        | ERENCE s                                                                                                                                                                   | 83 83 83 84 85 87 88 88 89 90 91                                     |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7                                                                                  | ERENCE s                                                                                                                                                                   | 83 83 83 84 85 85 87 89 90 91 92                                     |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.1.6<br>13.1.7<br>13.1.8                                    | ERENCE s ables Map 0 Table: User Space Map 1 Table: Configuration Space  sters PRTxDR PRTxIE PRTxGS PRTxDM2 DxBxxDR0 DxBxxDR1 DxBxxDR2 DxBxxCR0                            | 83 83 83 84 85 87 88 88 88 89 90 91 91                               |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.1.6<br>13.1.7<br>13.1.8<br>13.1.9                          | ERENCE s ables Map 0 Table: User Space Map 1 Table: Configuration Space  sters PRTxDR PRTxIE PRTxGS PRTxDM2 DxBxxDR0 DxBxxDR1 DxBxxDR2 DxBxxCR0 DxBxxCR0 DxBxxCR0 DxBxxCR0 | 83 83 83 84 85 87 88 88 89 90 91 92 93                               |

|        | N C REG<br>Regist<br>Regist<br>Registe | er Convention<br>er Mapping Ta<br>Register<br>Register<br>r Details<br>Bank 0 Regi<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.1.6<br>13.1.7<br>13.1.8<br>13.1.9<br>13.1.10               | ERENCE s                                                                                                                                                                   | 83 83 83 84 85 87 88 88 89 90 91 92 92 93                            |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11                                         | ERENCE s                                                                                                                                                                   | 83 83 84 84 85 87 88 88 89 90 91 92 93 93                            |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11                                         | ERENCE s                                                                                                                                                                   | 83 83 84 84 85 87 88 88 89 90 91 91 92 93 94 95                      |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11 13.1.12 13.1.13                         | ERENCE s                                                                                                                                                                   | 83 83 83 84 85 87 88 88 89 90 91 91 92 93 94 95                      |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11 13.1.12 13.1.13 13.1.14                 | ERENCE s. ables                                                                                                                                                            | 83 83 83 84 85 87 88 88 88 89 90 91 91 92 93 94 95 96                |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11 13.1.12 13.1.13 13.1.14 13.1.15         | ERENCE s. ables                                                                                                                                                            | 83 83 83 84 85 87 88 88 89 90 91 92 93 94 95 96                      |

|        | N C REG<br>Regist<br>Regist<br>Registe | GISTER REF er Convention er Mapping Ta Register Register r Details Bank 0 Regi 13.1.1 13.1.2 13.1.3 13.1.4 13.1.5 13.1.6 13.1.7 13.1.8 13.1.9 13.1.10 13.1.11 13.1.12 13.1.13 13.1.14 13.1.15 13.1.15 | ERENCE s. ables                                                                                                                                                            | 83 83 83 84 85 87 88 88 88 89 90 91 92 92 93 94 95 96 96 100 101 102 |

| 13.1.18 | CMP CR0         | 105  |

|---------|-----------------|------|

|         |                 |      |

| 13.1.19 | ASY_CR          |      |

| 13.1.20 | CMP_CR1         |      |

| 13.1.21 | ACBxxCR3        |      |

| 13.1.22 | ACBxxCR0        | 109  |

| 13.1.23 | ACBxxCR1        | .110 |

| 13.1.24 | ACBxxCR2        | .111 |

| 13.1.25 | ASCxxCR0        | .112 |

| 13.1.26 | ASCxxCR1        |      |

| 13.1.27 | ASCxxCR2        |      |

| 13.1.28 | ASCxxCR3        |      |

| 13.1.29 | ASDxxCR0        |      |

| 13.1.30 | ASDxxCR1        |      |

| 13.1.31 | ASDxxCR2        |      |

| 13.1.32 | ASDxxCR3        |      |

|         |                 |      |

| 13.1.33 | RDIxRI          |      |

| 13.1.34 | RDIxSYN         |      |

| 13.1.35 | RDIxIS          |      |

| 13.1.36 | RDIxLT0         |      |

| 13.1.37 | RDIxLT1         |      |

| 13.1.38 | RDIxRO0         |      |

| 13.1.39 | RDIxRO1         | 126  |

| 13.1.40 | 12C_CFG         | .127 |

| 13.1.41 | 12C_SCR         | .128 |

| 13.1.42 | I2C DR          | 129  |

| 13.1.43 | I2C MSCR        | 130  |

| 13.1.44 | INT CLR0        |      |

| 13.1.45 | INT CLR1        |      |

| 13.1.46 | INT CLR3        |      |

| 13.1.47 | INT MSK3        |      |

| 13.1.48 | INT MSK0        |      |

| 13.1.49 | INT MSK1        |      |

| 13.1.50 | INT VC          |      |

| 13.1.51 | RES WDT         |      |

| 13.1.51 | <del>-</del>    |      |

|         | DEC_DH          |      |

| 13.1.53 | DEC_DL          |      |

| 13.1.54 | DEC_CR0         |      |

|         | DEC_CR1         |      |

| 13.1.56 | MUL_X           |      |

| 13.1.57 | MUL_Y           |      |

| 13.1.58 | MUL_DH          |      |

| 13.1.59 | MUL_DL          |      |

| 13.1.60 | MAC_X/ACC_DR1   | 148  |

| 13.1.61 | MAC_Y/ACC_DR0   | .149 |

| 13.1.62 | MAC_CL0/ACC_DR3 | .150 |

| 13.1.63 | MAC_CL1/ACC_DR2 | 151  |

| 13.1.64 | CPU_F           | 152  |

| 13.1.65 | CPU_SCR1        | .153 |

| 13.1.66 | CPU SCR0        |      |

|         | sters           |      |

| 13.2.1  | PRTxDM0         |      |

| 13.2.2  | PRTxDM1         |      |

|         | PRTxIC0         |      |

| 13.2.4  | PRTxIC1         |      |

|         |                 |      |

13.2

|        |           | 13.2.5           | DxBxxFN                          | 159 |

|--------|-----------|------------------|----------------------------------|-----|

|        |           | 13.2.6           | DxBxxIN                          | 161 |

|        |           | 13.2.7           | DxBxxOU                          | 162 |

|        |           | 13.2.8           | CLK_CR0                          | 164 |

|        |           | 13.2.9           | CLK_CR1                          | 165 |

|        |           | 13.2.10          | ABF_CR0                          | 166 |

|        |           | 13.2.11          | AMD_CR0                          | 167 |

|        |           | 13.2.12          | AMD_CR1                          | 168 |

|        |           |                  | ALT_CR0                          |     |

|        |           |                  | GDI_O_IN                         |     |

|        |           |                  | GDI_E_IN                         |     |

|        |           |                  | GDI_O_OU                         |     |

|        |           |                  | GDI_E_OU                         |     |

|        |           |                  | OSC_CR4                          |     |

|        |           |                  | OSC_CR3                          |     |

|        |           |                  | OSC_CR0                          |     |

|        |           | 13.2.21          | OSC_CR1                          |     |

|        |           |                  | OSC_CR2                          |     |

|        |           |                  | VLT_CR                           |     |

|        |           |                  | VLT_CMP                          |     |

|        |           |                  | IMO_TR                           |     |

|        |           |                  | ILO_TR                           |     |

|        |           |                  | BDG_TR                           |     |

|        |           | 13.2.20          | ECO_TR                           | 104 |

| SECTIO | אם חופ    | ITAL SYSTE       | M                                | 185 |

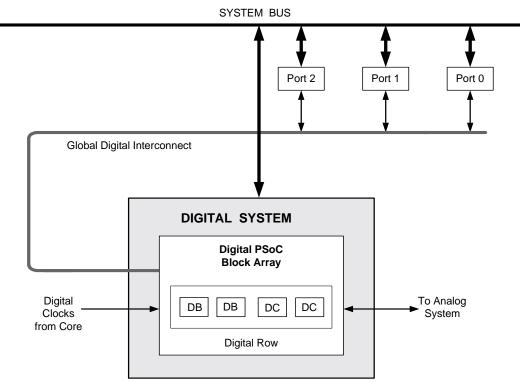

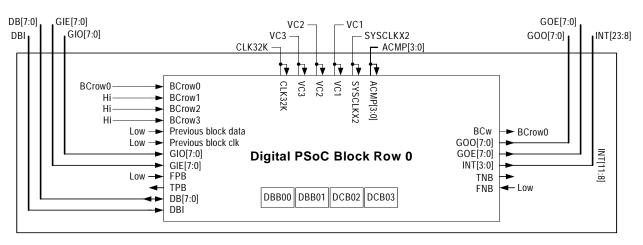

| OLOTIC |           |                  | hitecture                        |     |

|        |           |                  | mary                             |     |

|        | •         | •                | •                                |     |

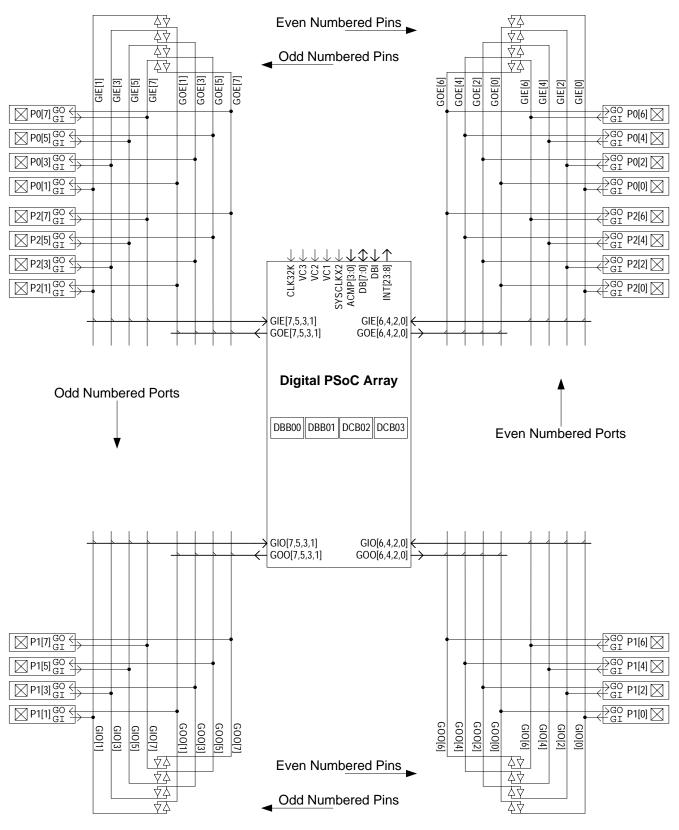

| 14.    |           |                  | onnect (GDI)                     |     |

|        | 14.1      |                  | Description                      |     |

|        | 14.2      | •                | initions                         |     |

|        |           | 14.2.1           | GDI_O_IN and GDI_E_IN Registers  |     |

|        |           | 14.2.2           | GDI_O_OU and GDI_E_OU Registers  | 189 |

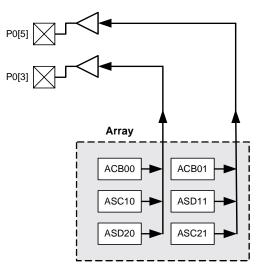

| 15.    | Arrav D   | igital Interco   | nnect (ADI)                      | 191 |

|        | 15.1      |                  | Description                      |     |

| 4.0    | D D:      |                  | •                                |     |

| 16.    |           | •                | nnect (RDI)                      |     |

|        | 16.1      |                  | Description                      |     |

|        | 16.2      | •                | initions                         |     |

|        |           | 16.2.1<br>16.2.2 | RDIxRI Register                  |     |

|        |           | 16.2.2           | RDIxSYN Register                 |     |

|        |           | 16.2.3           | RDIxIS RegisterRDIxLTx Registers |     |

|        |           | 16.2.4           | RDIxROx Registers                |     |

|        | 16.3      |                  | am                               |     |

|        |           |                  |                                  |     |

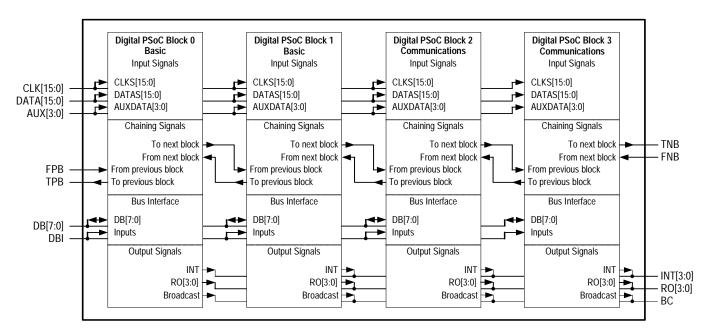

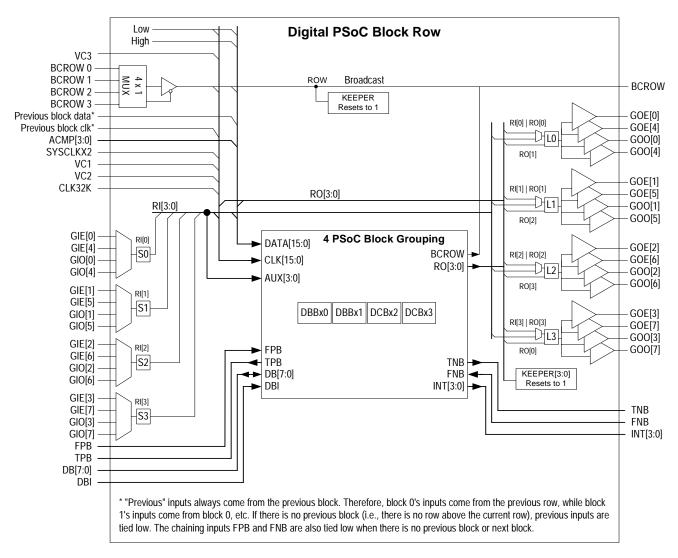

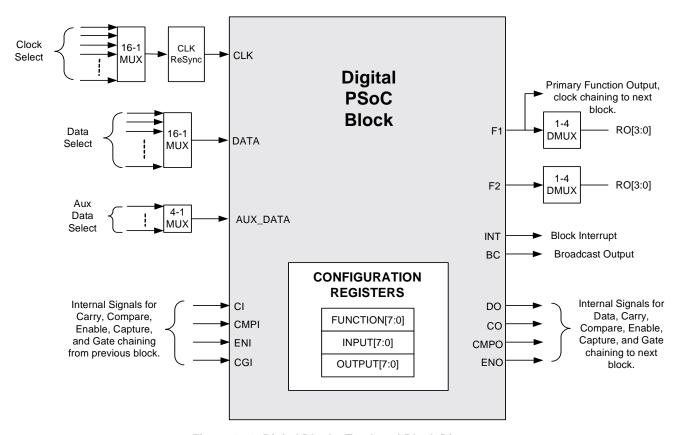

| 17.    | Digital I |                  |                                  |     |

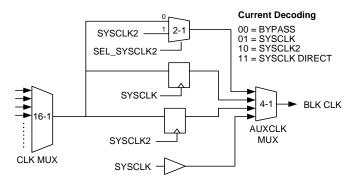

|        | 17.1      |                  | Description                      |     |

|        |           | 17.1.1           | Input Multiplexers               |     |

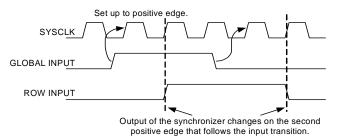

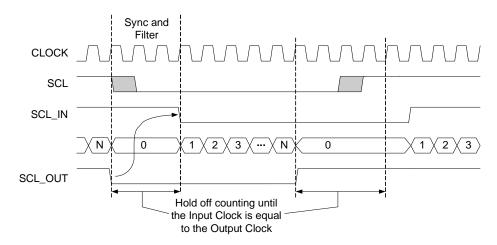

|        |           | 17.1.2           | Input Clock Resynchronization    |     |

|        |           | 17.1.3           | Output De-Multiplexers           |     |

|        |           | 17.1.4           | Block Chaining Signals           |     |

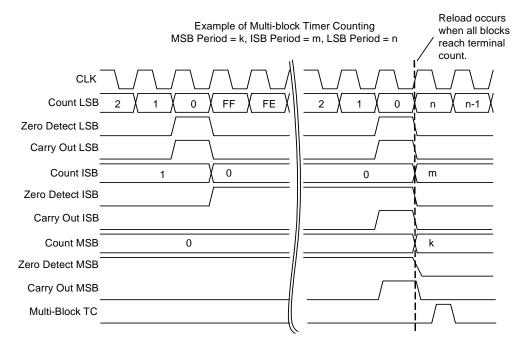

|        |           | 17.1.5           | Timer Function                   |     |

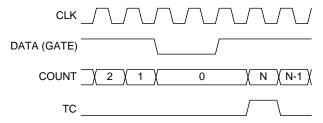

|        |           | 17.1.6           | Counter Function                 | 202 |

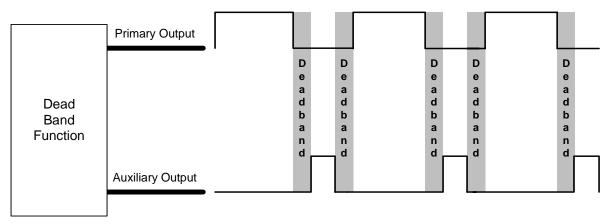

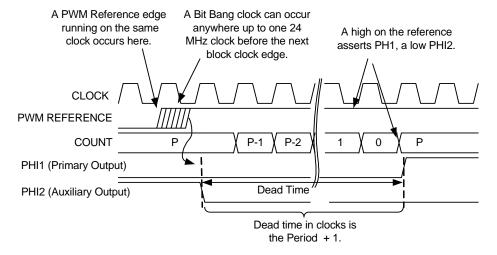

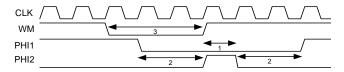

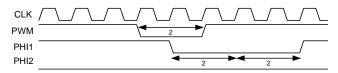

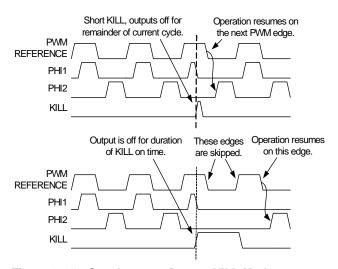

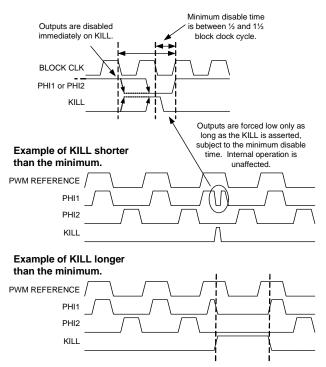

|      |                                     | 17.1.7                                                                                                                                                                                                   | Dead Band Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

|------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

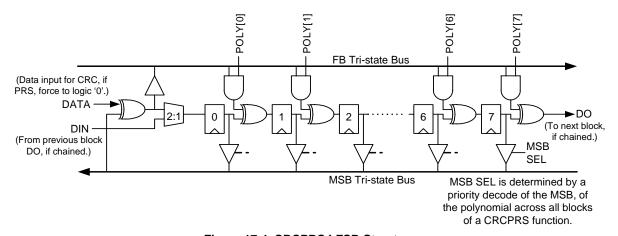

|      |                                     | 17.1.8                                                                                                                                                                                                   | CRCPRS Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

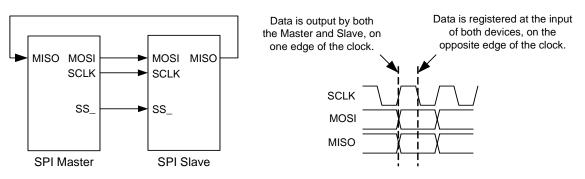

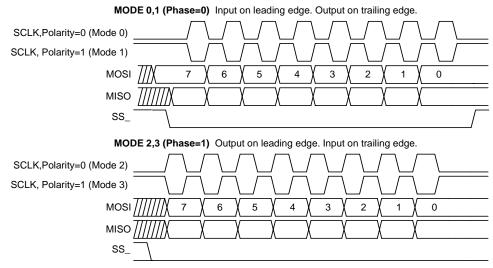

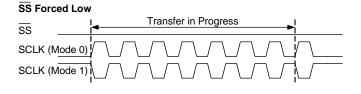

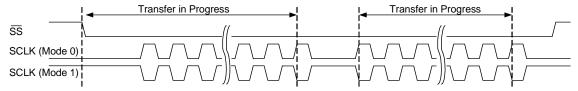

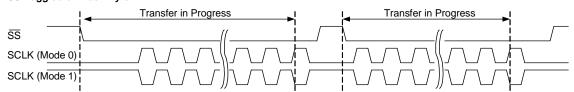

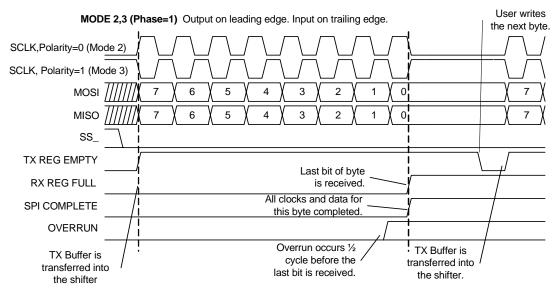

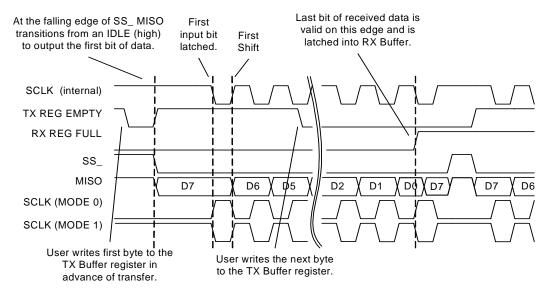

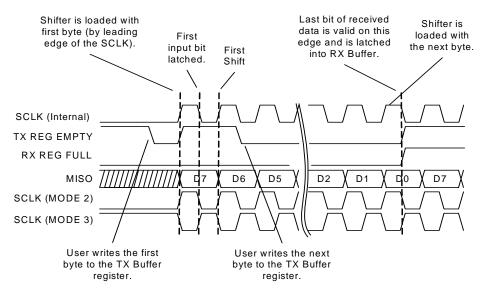

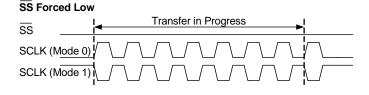

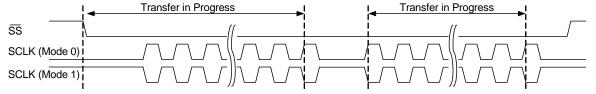

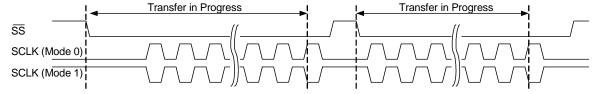

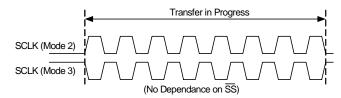

|      |                                     | 17.1.9                                                                                                                                                                                                   | SPI Protocol Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

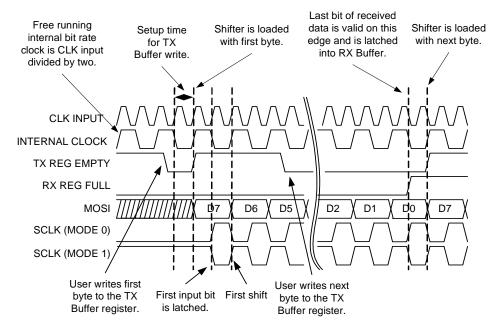

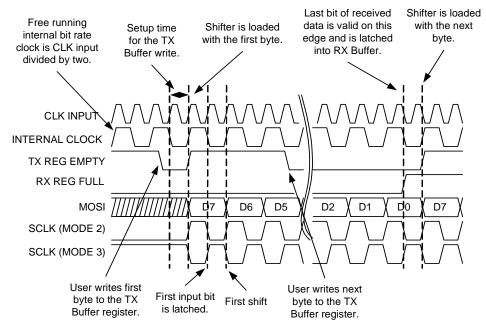

|      |                                     | 17.1.10                                                                                                                                                                                                  | SPI Master Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 206          |

|      |                                     | 17.1.11                                                                                                                                                                                                  | SPI Slave Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

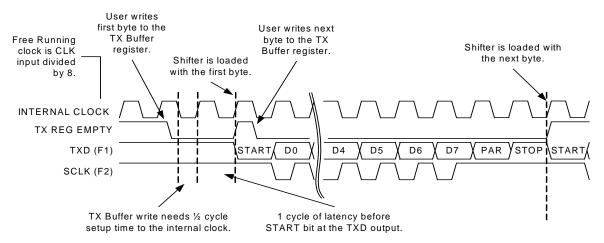

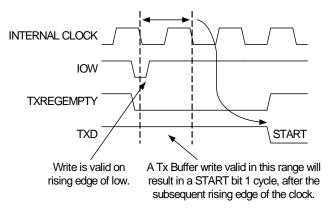

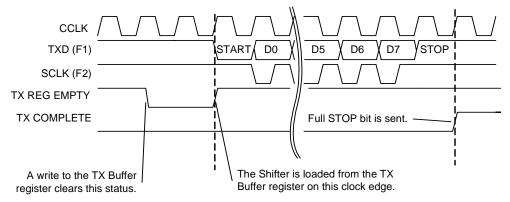

|      |                                     | 17.1.12                                                                                                                                                                                                  | Asynchronous Transmitter Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 207          |

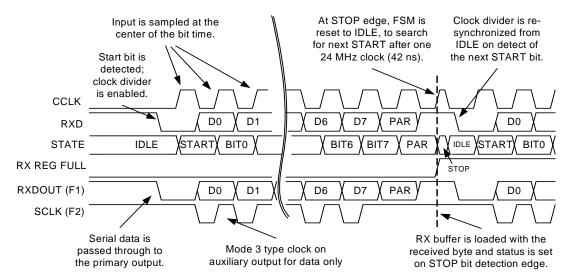

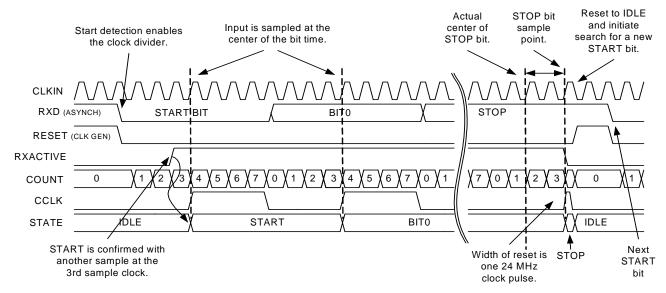

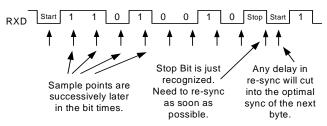

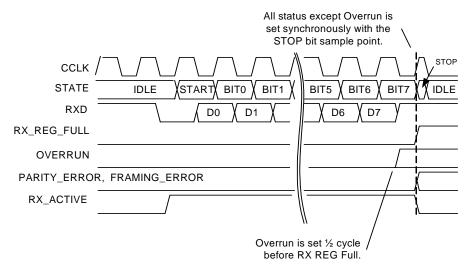

|      |                                     | 17.1.13                                                                                                                                                                                                  | Asynchronous Receiver Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 207          |

|      | 17.2                                | Register Def                                                                                                                                                                                             | initions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 208          |

|      |                                     | 17.2.1                                                                                                                                                                                                   | DxBxxDRx Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 208          |

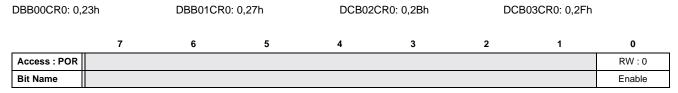

|      |                                     | 17.2.2                                                                                                                                                                                                   | DxBxxCR0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 213          |

|      |                                     | 17.2.3                                                                                                                                                                                                   | INT_MSK1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 213          |

|      |                                     | 17.2.4                                                                                                                                                                                                   | DxBxxFN Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 213          |

|      |                                     | 17.2.5                                                                                                                                                                                                   | DxBxxIN Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 214          |

|      |                                     | 17.2.6                                                                                                                                                                                                   | DxBxxOU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 214          |

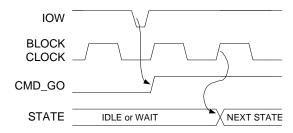

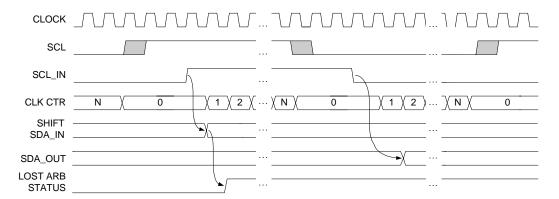

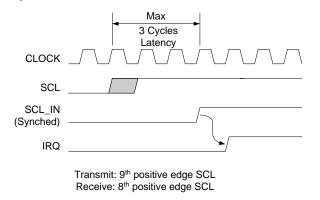

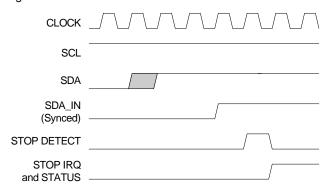

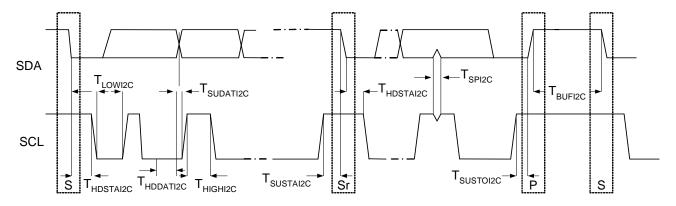

|      | 17.3                                | Timing Diagr                                                                                                                                                                                             | ams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 214          |